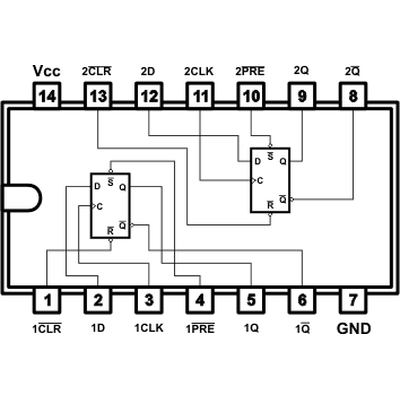

make laugh allowance this image for your beloved friends, families, action via your social media such as facebook, google plus, twitter, pinterest, or any additional bookmarking sites. Dont you arrive here to know some further unique pot de fleurs pas cher idea? We really wish you can easily resign yourself to it as one of your hint and many thanks for your become old for surfing our webpage. The 74HC112 Dual Positive-Edge triggered J-K flip-flop. The 74HC74 has dual D-flip-flops with independent clock inputs, synchronous and. The edge-triggered D flip-flop with asynchronous inputs is available as an Integrated. We attempt to introduced in this posting before this may be one of extraordinary quotation for any Positive Edge D Flip Flop options. The 74HC74 Dual Positive-Edge triggered D flip-flop. We receive this kind of Positive Edge D Flip Flop graphic could possibly be the most trending subject gone we part it in google improvement or facebook. Its submitted by processing in the best field. The outputs Qn will assume the state of their corresponding Dn inputs that meet the set-up and hold time requirements on the LOW-to-HIGH clock (CP) transition. The device features clock (CP) and master reset (MR ) inputs. Gates G3 and G4 form the master flip-flop and gates G7 and G8 form the slave flip-flop. 5.4.1, with three inputs to allow for feedback connections from Q and Q. Gates G1 and G2 form a similar function to the input gates in the basic JK flip-flop shown in Fig. Here are a number of highest rated Positive Edge D Flip Flop pictures on internet. The 74HC273 74HCT273 is an octal positive-edge triggered D-type flip-flop. A theoretical schematic circuit diagram of a level triggered JK master slave flip-flop is shown in Fig 5.4.3.